- 结合传感器的并行处理器实现高速成像

-

企业: 控制网 日期: 2008-04-17 领域: SCADA-RTU 点击数: 864 如果一幅图像的数据量相当于一千个字符,那么100,000幅图像的数据量有多大?能否设计一个数字成像系统来处理如此高帧速的图像。这样一个成像系统可以应用于机器视觉,智能视频系统,瞬间事件的科学分析,工业过程监控,互动游戏以及无人运输器和导弹的制导系统等众多领域。

2000年,来自匈牙利、西班牙和美国的科学家在布达佩斯成立了AnaLogic计算机公司。该公司的目标就是设计每秒能存储、分析和增强几千帧图像的数字成像系统。3年后,他们又在美国加利福尼亚州,伯克利城成立了AnaLogic的后继公司,Eutecus。在美国导弹防御局以及海军研究办公室的许可下,他们开发了Cellular Visual Technology(CVT).

CVT由大规模并行处理器和优化成像处理软件构成。有些实现方法使用一种创新的半导体制造工艺把图像传感器和并行处理阵列直接结合在一起,创造出一个多层芯片。图1是C-TON的照片。C-TON是第一款为商业市场设计的此类芯片。

公司首席技术官Dr Akos Zarandy和Dr Csaba Rekeczky 奔波于布达佩斯和伯克利之间。CVT技术的发明人,公司技术副主席,Zarandy10月份在秋季微处理器论坛上发表了关于CVT的技术介绍。这篇文章也吸取了该技术的另一名发明人,公司研发副主席Rekeczky的意见。

并非传统数字相机

Eutecus的设计与传统数字相机以及家庭摄像机大相径庭。经典的数字相机有CCD或CMOS成像传感器,这些传感器由微小感应单元组成的阵列覆盖而成。几乎每个感应单元都对应一个像素。在曝光过程中,照射到感应单元的光被转化为电。也就是说,感应单元将光子转化为电子。照射到感应单元上的光子越多,产生的电子越多,从而形成的像素越亮。经过模数转换,嵌在RISC核中的传统微处理器读取每个感应单元的值把像素聚合成图像。然后经过增强的图像被存储到照相机的闪存或其它存储媒介上之前。

传统数字相机的帧速很低,经常是几秒一帧而不是一秒几帧。处理器读取感应单元数据和聚合图像很费时间。为了解决这一问题,几乎所有的数字相机都有缓存。前一次曝光的数据就存在这些缓存中供处理器进行处理,以便相机进行下一次曝光。

家庭数字摄像机有更大的缓存。通过降低像素分辨率,它每秒可以处理25到30帧图像,满足PAL,SECAM或NTSC视频的要求。通过使用更大的成像传感器,高清晰度家庭数字摄像机可以录制更高帧速和画质更好的图像。当然,由于使用了更大的传感器,这种摄像机的价钱更高。但是,传统摄像机无法在超高帧速下录制和处理图像。

图像处理是实现高速成像的主要障碍:所有的光子几乎在同一瞬间到达各感应单元并被计入同一“时间窗”,但是聚合图像的处理器却是顺序处理这些数据。图像感应几乎是并行的,图像处理却不是。因此,从逻辑上解决该问题的方案是应用大规模并行处理。所以,每一个或每一组感应单元应该有专属的处理器。除此之外为了实现高速成像,Eutecus还应用了人眼视觉特性仿真的技术。

大规模图像并行处理

首先,我们要注意的是Eutecus为了达到梦幻般的帧速这一目标使用了大规模并行处理,但同时还是牺牲了像素的分辨率和色彩。这是在目前半导体技术水平下无法避免的。Eutecus最新的CVT感应处理器仅能处理64×64像素,8或16位灰度级或者完全黑白的图像。Eutecus相信在同样工艺结构下可以制造出处理能力达到256×256像素图像的芯片,大概是0.06兆像素。

与现今流行的10.2兆像素数字SLR (Single-lens Teflex)相比,CVT的分辨率看起来有些低。但是这种分辨率已经可以满足很多应用领域。例如,机器视觉,低分辨率的图像足以让机器人绕开小的物体和避免撞墙。在另一些应用领域中,与记录更多的细节相比,瞬间检测高速进程中变化的能力更重要。比如就有客户使用CVT成像系统研究玻璃摔碎瞬间碎片产生的过程。此外,和人类的眼睛关注视野中的细节一样,CVT可以通过对大的区域里所感兴趣的点进行快速计算来充分利用它有限的分辨率。

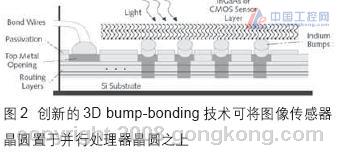

尽管在分辨率和色彩上做出了一些牺牲,CVT通过使用大规模图像并行处理获得的成就仍然令人印象深刻。芯片设计者可以用两种基本的方法实现这一技术。第一种方法可以传送最高帧速的图像。它是由单一芯片组成的,这种芯片使用一种3D bump bonding的技术在处理单元顶上加上图像感应单元。

如图2所示,在数以千计的微小铟凸点上,感应单元结合在处理单元顶部,构成了紧密连接在一起的多层芯片。传感器可以是传统的CMOS或CCD设备。但是,为了最大化性能,Eutecus使用了一种少见的材料—砷化铟(InGaAs)。砷化铟(InGaAs)感应器对光的敏感度比硅感应器高大约十倍,因此它们可以在更短的曝光时间中记录图像,从而满足高帧速的要求。处理器可以用传统CMOS工艺制造。

第2种实现CVT的基本方法是分别使用成像芯片和处理器阵列。逻辑上与第1种方法一样,但物理结构不尽相同。虽然有一个高速并行接口将成像传感器与处理阵列连接起来,但是与直接将传感器和处理器结合在一起的方法相比,这种方法还是慢了许多。受实现方式的限制,这种方法的最高帧速比第1种方法低了一到两个数量级(大约1000到10000帧每秒)。但是,两个芯片组合在一起的方式也有些好处:它可以使用更高分辨率的成像传感器,造价更低廉。而且,芯片设计者可以通过对ASIC掩膜或对FPGA编程等方式来实现并行处理器阵列。虽然FPGA只能生成少量的处理器阵列,但是可以大大减少投放市场的时间。

第3种实现CVT的方法是将成像感应单元阵列和并行处理器阵列合成在同一晶圆上,和多层芯片方式比起来,这种方式的两个阵列结合的更紧密。但是,目前的半导体技术无法实现这一方法。因为即使都使用CMOS制造,成像传感器和ASIC的设计与制造参数也不同。另外,将感应单元和处理器单元结合在一起将会降低阵列的密度,从而降低芯片的分辨率。而且,阵列单元的光通道将更小,降低了它们的敏感度。尽管如此,该方法仍是未来研究和发展的主要方向。

克服制造的缺点

传感器阵列没有什么新奇,因此我们把注意力集中到处理器阵列上。Eutecus将几十个处理单元紧密的结合在一起,各单元之间可以相互联系。图3是C-TON的图片。这一设计共有8×8,64个处理单元。其他的设计的处理器阵列大小不尽相同。(早期的有4×4阵列)。 每个C-TON芯片的单元从64个感应点接受图像数据,所以图像的分辨率是64×64。全局控制处理器是一个8位微控制器。全局控制器负责处理片外I/O以及向阵列传输程序指令。C-TON有2K的全局程序存储空间,由传统的0.18微米CMOS制造,工作频率为100MHz。它的有32位I/O总线,工作频率也是100MHz,带宽400MB/s。

每个单元内部有一个基于单指令多数据的24位处理器,其结构专门为图像处理进行过优化。一个多路复用器接收所有连接到这一单元的感应点的输出,然后将信号输送到一个通用8位模数转换器。这些模数转换器依次连接到处理器上。此外,每个单元和另一个单元共享1k局部内存,每个单元与和它相邻的单元之间有通信接口。单元之间可以通过共享内存来进行通信,每个时钟周期传输8bits数据。不相邻的单元之间没有直接联系。

需要注意的是,像C-TON那样将成像传感器和处理器结合在一起的芯片,未经处理的数据通过数以千计的铟凸点而不是由传统的I/O总线从感应器传输到处理器阵列的。每个单元和在它顶部的感应点之间有专属的I/O接口,这一巧妙的设计解决了大规模处理阵列常有的问题:如何通过大规模阵列传输数据。

另一些大规模并行设计通过阵列的边缘接收数据,通过网络传输数据。但是在“凸点键合”多层芯片中,图像数据可以瞬间到达阵列的任何一点,不用绕道没有延迟。当然,图像数据I/O输出是仍需穿过整个阵列。但是,通过在本地处理图像数据,处理单元可以减少从芯片输出的未经处理的图像数据。

阵列各层的资源分配

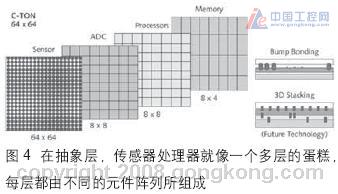

像C-TON这样将传感器和处理器结合在一起的芯片从抽象的角度说有多层硬件资源:成像传感器,多路复用器,ADC,处理器以及存储器。成像感应器由独立的凸点键合的晶圆组成的。多路复用器和ADC是混合信号部件,一层独立的晶圆。处理器和SRAMS占用同一层晶圆的一部分,同样使用数字CMOS技术制造。图4是各层的示意图视。

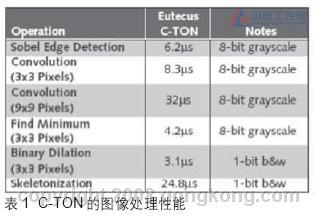

单元内部的处理器有ALU,形态单元和比较单元。24位ALU进行8或16位算术操作(加,减,乘),形态单元负责对黑白图像进行简单的1位操作并辅助ALU处理灰度图像。处理器每个时钟周期处理器执行一条指令,可以从单元存储器,和相邻单元公用的存储器以及成像传感器这3处读取数据。表1给出了C-TON进行简单图像处理时的性能数据。

虽然阵列中的所有单元必须运行同样的程序,但是通过使用数据驱动处理(data-driven)和bit-mashing技术可以让每个单元处理像素时有微小的差异。这也是将感应点和处理器在阵列中直接键合的优点。图5展示了对独立像素进行特殊操作的好处。通过独立调节每个像素,处理器可以有效的扩展图像的动态范围重新捕获丢失的色彩和细节。

为了降低能耗,Eutecus在处理器阵列中使用了扩展时钟门,不工作的处理器可以关闭。Eutecus表示,工作频率为100MHz的C-TON全部处理器工作的最大耗电量为300mW,最低可以低于50mW。这使得C-TON适用于电池供电的系统。然而,由于传感器发热产生“热“像素,散热就成为了这一设计潜在的问题。当成像传感器发热时生成的图像噪点较多,特别是在图像较暗的部分。不过开发人员可以用图像处理器增大信噪比来减少这种影响。

众多应用

Eutecus的技术可以应用于众多领域,C-TON这个Eutecus技术的早期应用例子,只是其中之一。阵列的大小以及每个单元对应的感应点数都不是一成不变的。根据设计的需要,一个单元既可以像C-TON一样处理8×8像素块的数据,也可以只处理单个像素。早期0.18微米CMOS制造的模型芯片只能处理32×32个像素。

下一代设计可以像ASIC一样,用90nmCMOS实现处理器阵列,而不用把成像传感器键合到晶圆上。芯片将使用传统的32位I/O总线和传感器通讯。Eutecus表示,双芯片运行方式可以拥有180×180的处理器阵列,运行时钟120MHz,支持最大720×720的分辨率。该设计将通过牺牲帧速来提高分辨率,降低制造成本。尽管如此,该设计仍可每秒捕获1000帧图像并对图像进行一些形态操作。

然而,Eutecus的目标并不是成为一个无晶圆半导体公司。其主要商业模式是发放类似于软IP的CVT技术许可。为了实现这一目标,Eutecus为客户提供处理器阵列及相应部件,它们就像合成的VHDL模型,顾客可将其嵌入到自己的ASIC或FPGA中。Eutecus提供的开发工具可以让客户设计所需的任何大小的阵列。公司还提供为图像处理优化过的“Instant Vision”功能库,供客户进行软件开发。该库的初等函数用组合语言编写,客户可以使用高级语言如C,C++编写应用软件。

由于在可编程逻辑芯片中无法整合成像传感器,如果对FPGA编程来生成处理器而不是对ASIC进行掩膜生成处理器,那么就需要片外传感器。而且,由于FPGA的性能局限,处理器阵列的大小有所减少。然而,与制造一个ASIC相比,对FPGA编程更快更便宜。 有一个这样的设计,它在Xilinx Virtex-4LX中生成一个20×20的处理器阵列。全局控制处理器是RSIC或在同一FPGA中生成的DSP核。在150MHz的工作频率下,这一设计每秒可执行600亿条指令,最大图像分辨率为160×160像素(每个处理器64个像素)。Ectecus公布的最大帧速为每秒3000帧。

有一个这样的设计,它在Xilinx Virtex-4LX中生成一个20×20的处理器阵列。全局控制处理器是RSIC或在同一FPGA中生成的DSP核。在150MHz的工作频率下,这一设计每秒可执行600亿条指令,最大图像分辨率为160×160像素(每个处理器64个像素)。Ectecus公布的最大帧速为每秒3000帧。

视觉仿真

如果客户对帧速的要求比较低,双芯片实现方式除了降低费用,缩短投放市场的时间外还有一个优势:一个独立的感应器可以比多层芯片有更高的图像分辨率。通过模仿人类视觉的某些特性,开发人员实现更高的分辨率。

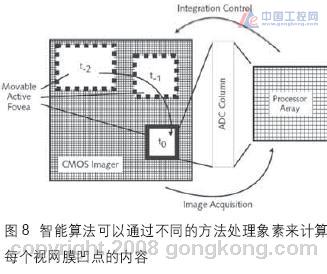

传统的数字图像处理器往往扫描整个图像,而很少或根本不关注图像的细节。但是我们用另一种方式观察图像:眼睛迅速的扫过整个图像,找出一些关键点,快速的形成一副要素图。科学家称之为“快速跳跃”。这是必须的,因为虽然我们的眼睛可以观察一个大约210度的广阔的视野,但是在每一刻我们只能聚焦于其中的一小部分。这个点叫做视网膜凹点,是我们大脑分析能力最集中的一点。而周边的视觉主要是用来检测运动或照度的突然变化,这些变化能传达潜在的威胁。图7说明了快速视觉和传统视觉的不同之处。 当CVT阵列无法实时处理成像传感器的像素时,开发人员可以通过处理小区域的像素的方法来模仿人类视觉的快速跳跃。事实上,处理阵列就相当于视网膜凹点,从传感器的一部分跳到另一部分。智能算法可以通过用不同的方法处理像素来计算每个视网膜凹点的内容。第一步是在低分辨率下扫描全图找到可能感兴趣的点,或者用软件比较相邻的帧,找出变化的部分,然后放大该区域。图8显示了这一过程。

当CVT阵列无法实时处理成像传感器的像素时,开发人员可以通过处理小区域的像素的方法来模仿人类视觉的快速跳跃。事实上,处理阵列就相当于视网膜凹点,从传感器的一部分跳到另一部分。智能算法可以通过用不同的方法处理像素来计算每个视网膜凹点的内容。第一步是在低分辨率下扫描全图找到可能感兴趣的点,或者用软件比较相邻的帧,找出变化的部分,然后放大该区域。图8显示了这一过程。

智能视频监控,是Eutecus一直在寻求的CVT技术的商业应用。通过程序控制,摄像机可以检测广阔视野中的运动,然后放大任何运动的物体,进一步的分析它。如果摄像机发现了感兴趣的东西,它可以向保安发出警报。用合适的软件监控运动,摄像机可以自己做出判断而不用像现在那样依靠中央计算机进行监控或把图像传电视墙由安保人员来监控。

智能视频监控,是Eutecus一直在寻求的CVT技术的商业应用。通过程序控制,摄像机可以检测广阔视野中的运动,然后放大任何运动的物体,进一步的分析它。如果摄像机发现了感兴趣的东西,它可以向保安发出警报。用合适的软件监控运动,摄像机可以自己做出判断而不用像现在那样依靠中央计算机进行监控或把图像传电视墙由安保人员来监控。

这可不是科幻小说里的情节,某些传统的数字摄像机已经可以进行简单的实时图像分析。例如Canon和Fuji研制出了供普通消费者使用摄像机,这种摄像机在其视野内最多可以监控10个面孔。这种摄像机还可以锁定监控对象,调节曝光。Eutecus的超高帧速和单一像素处理技术大大提高了智能视频监控的可行性。

然而,编程人员必须做出一个选择:软件进行的分析越多,处理每幅图像所用时间越多,从而降低了帧速。如果一个程序控制工作频率为100MHz的C-TON芯片达到每秒处理100000帧图像的峰值阵列中的每一个处理器只有10微秒来分析和修改像素。如表1所示,C-TON可以在如此短的时间内完成这些简单的操作,但是要完成更复杂的任务就需要降低帧速或使用更快的芯片。

为超高帧速编写程序的人员将使用组合语言而不是调用C++中预先写好的函数。目前,Eutecus和其早期客户密切合作开发软件。Eutecus承认,将来低级开发工具是必需的。

Eutecus正在进入市场

Eutecus生产了一个有4×4处理器阵列的早期模板芯片。这一概念芯片包含一个可以捕获32×32像素的凸点键合成像传感器。更先进的C-TON工程样品芯片正在进行测试,这种芯片拥有8×8处理器阵列,64×64像素成像传感器。这些芯片都证明了Eutecus的技术是可行的,当用户掩膜ASIC或对FPGA编程时,Eutecus将帮助用户设计产品和编写软件。公司的主要目标是发放IP许可。Eutecus正在打造其IP块的第一个版本:一个用于ASIC实现方式,一个用于FPGA实现方式。而其改进版将在本季度完成。于此同时,Eutecus还在开发其第一个瞬间可视图像软件开发库。共有信号处理,图像处理,多目标跟踪以及特征识别4个库。此外,Eutecus还提供了一个开发系统,该系统为用户提供了一个供用户参考的智能监控摄像机设计范例。

超高帧速传输技术非常专业化,但是这并不意味着该技术的市场范围非常小。相反,鉴于以前的先例,MPR认为超高帧速传输技术将为开发人员带来灵感,引发从未出现过甚至从未有人想像过的应用。

当1839年Louis Daguerre发表基本摄影技术时,世界对其用银版照相法捕捉逼真影像的能力大加称赞。但是由于技术局限,早期还无法捕捉瞬间景象。18世纪末,宽孔径镜头和更敏感的感光乳剂的出现使得瞬间曝光得以实现。瞬间摄像从技术上来说仅仅只是改进,但从应用角度来说,这和摄影技术的发明一样是一次革命。这项技术使人类摆脱了时间的限制,可以观察到飞行的生物以及从未见过的景象。最著名的例子就是Eadweard Muybridge用暂停动作图像证明了马在奔跑的时候四蹄同时离地,这一结果画家们几个世纪以来从来没有观察到。

20世纪,使用模拟技术的高速摄影进一步扩展了人类的视野。Harold Edgerton用电子闪光捕捉到子弹穿过苹果的图像。专用高速胶片摄像机为我们展示了水滴的形态以及核弹爆炸时可怕的景像。但是,在过去这些摄制这些图像不但需要昂贵的设备,还受到机械影像传输的限制。摄像机无法反映出其所摄的景象。

超高速自适应摄像是21世纪摄像技术的一次革命。很快,普通消费者负担的起的摄像机将被研制出来。这种摄像机可以摄取生物无法察觉到的事物。过不了多久,这种摄像机将被用作被动监视器。将传感器阵列和处理其阵列结合在一起是一个令人印象深刻的技术创新,因为它可以在感应成像的同时处理图像。

和其它新技术一样,高速数字成像技术的应用既令人兴奋又令人恐惧。但是它是人类感知的一次扩展,为智能化机器的设计提供了一条新路。

----摘自工控网

|

|

|

|

|

|

- 下载排行更多»

-

- 1Power Panel宣传样本

- 2公司形象手册

- 3工业PC宣传样本

- 4集成自动化宣传样本

- 5驱动器产品概览样本

- 6贝加莱CNC技术

- 7电机与减速器产品概览

- 8变频器样本

- 9移动车辆及工程机械自动化

- 10Automotion 2013-03

- 11印刷行业专刊(2013)

- 12培训模块之 TM213-自动化操作系统(Runti..

- 13培训模块之 TM210-Automation Studio 3.0..

- 14操作面板和工业PC选型手册

- 15电机和减速器选型手册

- 16APROL DCS宣传样本

- 17APROL EnMon宣传样本

- 182013年菲尼克斯电气德国汉诺威展会精彩回顾

- 192013年菲尼克斯电气德国汉诺威展会报道-4..

- 202013年菲尼克斯电气德国汉诺威展会报道-4..

- 212013年菲尼克斯电气德国汉诺威展会报道-4..

- 222013年菲尼克斯电气德国汉诺威展会报道-4..

- 在线反馈

| 1.我有以下需求: | |

|

|

|

| 2.详细的需求: | |

| * | |

| 姓名: | * |

| 单位: | |

| 电话: | * |

| 邮件: | * |

.jpg)